# ROLE OF VHDL IN DIGITAL SYSTEM DESIGN

Mr. R.P.RAGHATATE<sup>1</sup> Mr. ASHISH S. MORE2, Mr. AKASHDEEP A. JIWANE<sup>3</sup>, Ms. SHWETA M. PANGUL<sup>4</sup>, Acharya Vinoba bhave institute of technology ,Pawnar Wardha

#### ABSTRACT

This paper describes the design and implementation of 4x1MUXandALUusing VHDL results include successful compilation of VHDL code in QuartusII, waveforms shows verification of truth table, the result are also verified in analog domain using analog simulation it also show layout level implementation of 4x1 MUXand ALU usingmicrowind tool, it also shows technological view of 4x1 MUXand ALUalong with chip floor plan. Keywords -4x1 MUX,ALU, VHDL, Analog, Layout, Chip floor plan

#### I. INTRODUCTION

The term digital system include the various system from low level component to complete system over a chip and board –level design .Considering a digital system and its complexity it is not possible to understand such a complex system completely, so to make design of a system less complex and understandable VHDL is used .This paper describes the implementation of 4x1 MUXand ALU using VHDL technology which meets less complexity requirement ,it also shows how efficiently digital system i.e.4x1 MUXand ALU is implemented up to layout level results shows technological map, RTL view, chip floor plan chip layout ,output waveforms showing voltage Vs time relations and verification of truth table .

### II. 4X1 MUX DESIGN

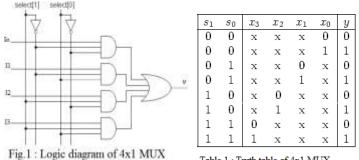

4x1 mux is a combinational circuit that has anability to increase the amount of 4 bit data that can be sent over the network within a certain amount of time andbandwidth.A4 bit input provides using 2 select linesand produce a proper output. Fig (1) shows logic diagram of 4x1 muxtable (1) shows truth table of 4x1 mux. A multiplexer is also called a dataselector.In analog circuit design, a multiplexer is a special type of analog switch that connects one signal selected from several inputs to a single output.In digital circuit design, the selector wires are of digital value.

Table 1 : Truth table of 4x1 MUX

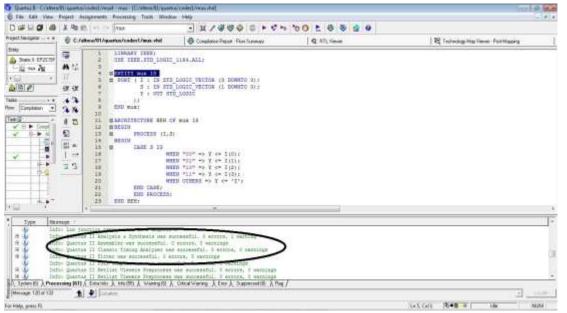

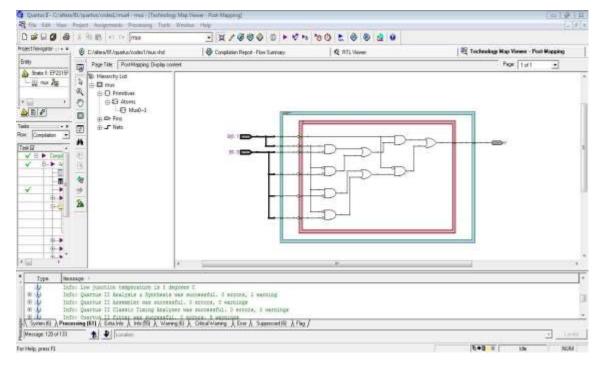

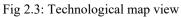

## Fig 2.1: VHDL Code compilation

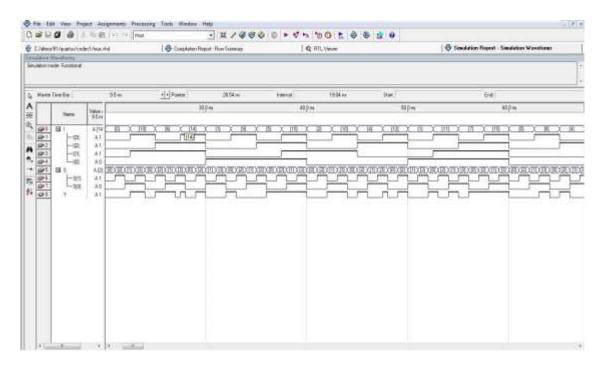

## Fig2.2: Output waveform

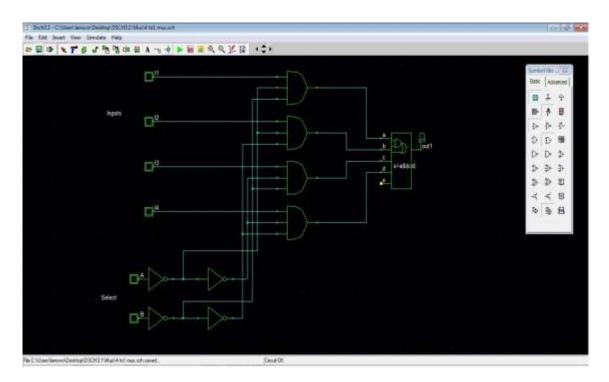

Fig2. 4: Schematic of 4x1 MUX beforeexecutioninanalog domain

010203

Fig 2.5: Schematic of 4x1 MUX afterexecution in analog domain

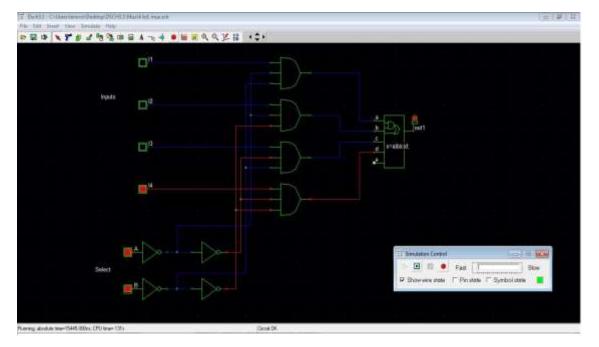

Fig 2.6: Layout of 4x1 MUX circuit

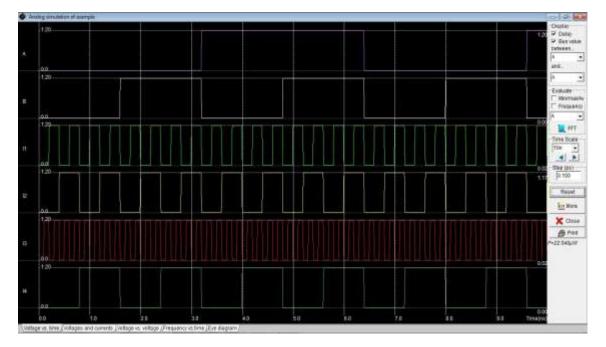

Fig 2.7: Voltage VS Time relationship in analog domain.

# III. ALU DESIGN

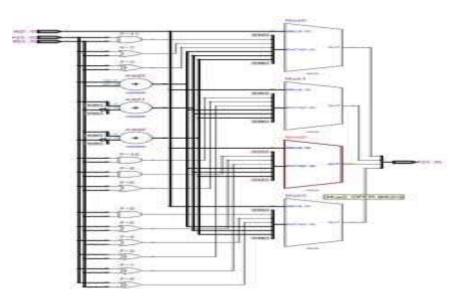

Fig3: Logical diagram of ALU

An arithmetic and logic unit (ALU) is a digital circuit that performs integer arithmetic and logical operations. The ALU is a fundamental building block of the central processing unit of a computer,

| Operation | Mode Select Inputs |    |            | Output      |

|-----------|--------------------|----|------------|-------------|

|           | S2                 | S1 | <b>S</b> 0 | F           |

| Clear     | 0                  | 0  | 0          | F = 0 0 0 0 |

| B – A     | o                  | 0  | 1          | F = B – A   |

| A – B     | 0                  | 1  | 0          | F = A – B   |

| ADD       | o                  | 1  | 1          | F = A + B   |

| XOR       | 1                  | 0  | 0          | F = A XOR B |

| OR        | 1                  | 0  | 1          | F = A OR B  |

| AND       | 1                  | 1  | 0          | F = A • B   |

| Preset    | 1                  | 1  | 1          | F = 1111    |

Fig(a): Functional table of ALU

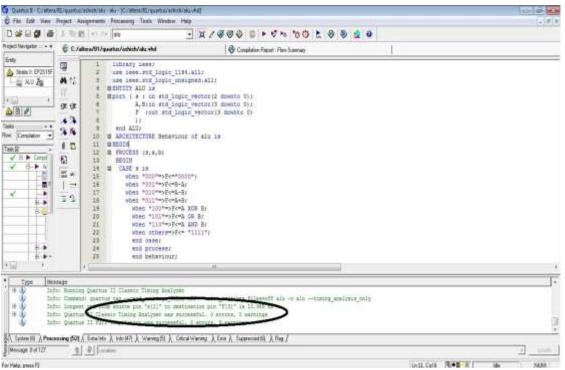

Fig 3.1: VHDL Code compilation

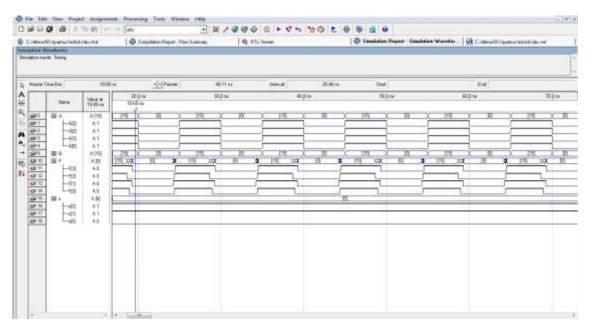

# Fig3.2: output waveform

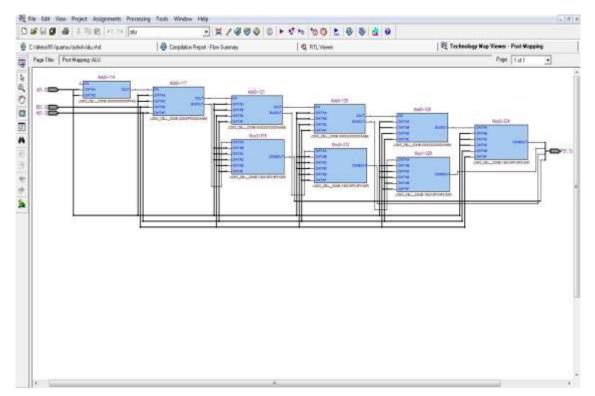

Fig 3.3: Technological map view

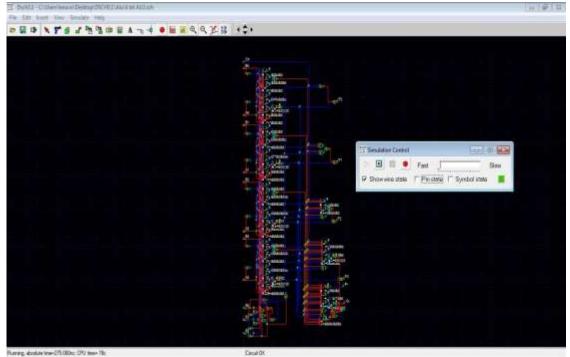

Fig 3.4: Schematic of ALU after execution in analog domain

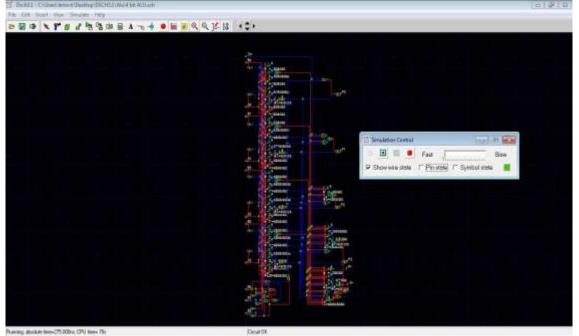

Fig 3.5: Layout of ALU circuit

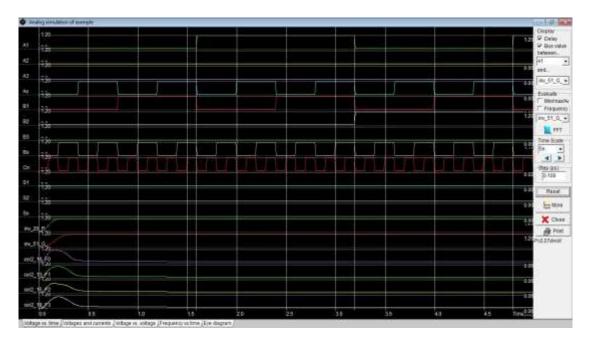

Fig 3.6: Voltage VS Time relationship in analog domain.

# **RESULT ANALYSIS**

From the above experimental work we can observe that designing a combinational & sequential circuit in analog domain is complicated than designing a same circuit in digital domain. If we observe carefully the design of less complex circuit in analog as well as in digital domain is not difficult, also it is easier to debug the error. but as we move on to complex circuit design e.g. ALU ,it can been seen that designing in analog domain is very difficult as well as time consuming also it is very difficult to locate and debug the error if any .We are designing this project in analog and digital circuit. The main purpose of the project is to design a complex circuit is in the simple form. Here have designed combinational circuit i.e. mux or adder, this circuit is very simple to design and the time consumption is very less and it is very easy to locate and debug the error if any, and if we designing a 4 bit ALU having complex logic circuit, its design in analog domain is very complex and it is time consuming also it is difficult locate and debug the error so to avoid this problem we have used designing in digital domain

# CONCLUSION

CMOS 90nm model is used to design a layout of ALU and4x1 MUX. Simulation results shows successful compilations of VHDL code and its conversion into Verilog file which is used to make a layout using microwind tool. Tools used are QuarutsII, Dsch&microwind. From both performance standpoint and cost standpoint, these results show that CMOS is very competitive with available technologies.

From the overall above discussion we can conclude that VHDL plays a key role in digital system design also working in digital domain or designing circuit in digital domain is more efficient, convenient and less time consuming as compare to analog domain, here in this paper we have studied the role of VHDL in digital system design also we have design and simulated some combinational circuit to show the comparative analysis in working with analog and digital domain. The simulations are done directly using the Quartus II tool for digital domain and Dsch and Microwind tool for analog domainThere is an immense scope for further work in the field of circuit design & simulation with VHDL.

010203

# REFERENCES

- Rupesh Prakash Raghatate1,Swapnil S.Rajurkar2,Priyanka U Badhe3, Pravin L.Turale4,"Design and Implementation of Full Adder Using Vhdl and Its Verification in Analog Domain" International Journal of Engineering Science Invention ISSN (Online): 2319 – 6734, ISSN (Print): 2319 – 6726 www.ijesi.org Volume 2 Issue 4 || April. 2013 || PP.35-39

- 2. Bhaskar, J of A VHDL Primer.PHI (2012).

- 3. Brown, S & Rose, T. Architecture of FPGAs and CPLDs.

- 4. Brown, S and Vranesic, fundamentals of DIGITAL LOGIC with verilogdesign.TMH (2009).

- 5. Nimje, A, R, Design and Implication of some digital sequence detector network, project report M.Sc II (Ele.).

- 6. Pedroni, V, A, CircuitDesign and Simulation with VHDL.PHI(2012)

- 7. Roth, C, H, Digital System Designed using VHDL, (2008).